This module consists of several parts, a pulse divider with integer divisions between 2 and 8, and several logic elements. The divider is used to generate interrelated pulses for use in creating poly-rhythms, and unusual sequences. It can also be run at audio frequencies as a sub-oscillator/sub harmonic generator. The output pulse from each division is one clock cycle in length, and the relationship between pulses is fixed. Specifically, the /4 output will correspond to every second pulse from the /2 output. Likewise, the /8 will correspond to every second pulse from the /4 output, and the /6 will correspond to every second pulse from the /3 output. Needless to say, the /2 and /3 groups are not related to each other, or to the /5 or /7 outputs. All however share a common external reset, so they can be synchronized. All outputs go high on reset. As well as the pulse divider, there are also five boolean logic elements. Two are basic inverters. If you apply a LOW (e.g. a gate output in its OFF state) they will give a HIGH (gate ON) output, and vice versa. The OR gate has two inputs, and gives a HIGH whenever one or both inputs are HIGH. The AND gate has two inputs, and gives a HIGH only when both inputs are HIGH. The fifth is an exclusive OR gate (XOR), giving a LOW when both inputs are within 1.2 volts of each other, and a HIGH when they are not. The OR, AND and XOR also offer inverted outputs, giving the option of using them as NOR, NAND and XNOR gates. Unlike the Analog Logic module, these are for processing gate, trigger and clock signals, although the XOR gate can accept linear inputs as well. Some ideas on how to use this module: Feed a clock signal into the input of the pulse divider. The divided signal is available simultaneously for each output. If running at audio frequencies, feed some of these to a mixer or other signal processing device. If running at low speed, try driving two different sequencers at the same time from different divisions. Try feeding the /8 output into the reset - this will force all to synchronize to a /7 count, with the lesser divisions becoming "syncopated". The AND gate could be used to control a clock signal. If the second input is LOW, no clock signal passes. If the second input is high, the signal passes unimpeded. Of course, there are a lot more things that can be done with the logic gates. For example, the /6 and /7 outputs could be ANDed together, and that would give a pulse every 6 x 7 (42) clock pulses (i.e. 1 pulse immediately the pulse divider is reset, and the second 42 pulses after that etc.). A little on how it works:

The clock and reset signals are processed by the TL072. The reset is sensitive to rising edges only, meaning that a continuous gate signal would initially reset the dividers, then allow the module to continue counting. The Reset button on the other hand is wired so that holding it in will stop all counting, and hold all outputs high for as long as the button is held. Following the input processor are four 4017 decade counters wired to give the various divisions. Where possible, sub-divisions have been taken from the same chip, with the various pulses being ORed together by diodes. Each output is buffered by an emitter follower. Many different types of small signal or switching transistors (e.g. BC547) can be used here without affecting the performance. The boolean logic are simple discrete R/DTL designs. When either input of the OR gate receives a voltage high enough, the first transistor is switched on, pulling the base of the second transistor low, and thus turning it on as well. This results in the output being pulled up to the voltage governed by the resistor divider. In the case of the AND gate, both input transistors must be turned on before the output transistor can be turned on, as the input transistors are in series with each other. The inverters are basically just the same as the first stage of the OR gate, with the exception of there being only one input. Further explanation of how the Exclusive OR gate works can be found here. Construction

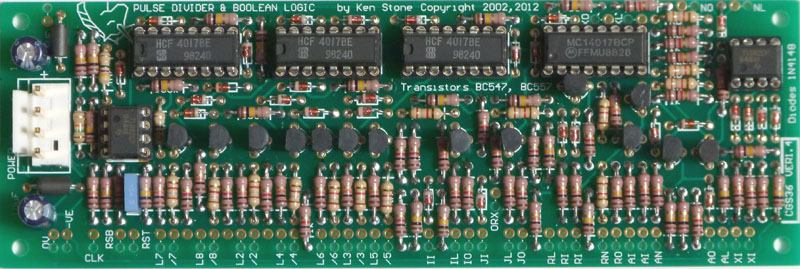

The component overlay. Click here for an enlarged printable version. VER1.4 PCBs have the upper part of the output dividers marked as RA, RB, RC, RD and RE on the PCB. These resistors are 1k8 for +/-15V operation and 1k5 for +/-12 volt operation. Check your output voltages when you have assembled them. Ideally the voltages will swing between 0 volts and +5 volts. Some small variance either way is nothing to be concerned about. The LED resistors (RL) can be selected as needed. If you are using common LEDs, 1k to 2k2 would be appropriate. If you are using any of the super-bright modern LEDs for their unique colors, the resistors can be much higher, 10k to 33k for example, so that the LEDs don't dazzle you.

Notes:

CGS36 Tutorial By Nicholas Peck At 'Under The Big Tree' Parts list This is a guide only. Parts needed will vary with individual constructor's needs. Article, art & design copyright 2001 by Ken Stone |